数电设计-八路抢答器

1设计要求设计一个能支持八路抢答的智力竞赛抢答器;主持人按下开始抢答的按键后,有短暂的报警声提示抢答人员抢答开始且指示灯亮表示抢答进行中;在开始抢答后数码管显示30秒倒计时;有抢答人员按下抢答键后,在数码管上显示抢答成功人员的编号,倒计时暂停,同时后续抢答人员的抢答将无效;当主持人再次按下按键回到复位状态,倒计时的数码管保持显示30,显示人员编号的数码管灭,指示灯灭。利用数字电路设计一个八路抢答器

1 设计要求

设计一个能支持八路抢答的智力竞赛抢答器;主持人按下开始抢答的按键后,有短暂的报警声提示抢答人员抢答开始且指示灯亮表示抢答进行中;在开始抢答后数码管显示30秒倒计时;有抢答人员按下抢答键后,在数码管上显示抢答成功人员的编号,倒计时暂停,同时后续抢答人员的抢答将无效;当主持人再次按下按键回到复位状态,倒计时的数码管保持显示30,显示人员编号的数码管灭,指示灯灭。

利用数字电路设计一个八路抢答器,允许八路参加,并具有锁定功能,用LED显示最先抢答的队号码,系统设置外部清除键,按动清除键,LED显示器自动清零灭灯。数字显示功能:数字抢答器定时为30S,启动开启键以后要求Ⅰ)定时开始;Ⅱ)扬声器要短暂报警;Ⅲ)发光二极管亮灯;如果在30S内抢答有效,计时结束,30S内抢答无效,发光二极管灯灭。

1.1 设计电路

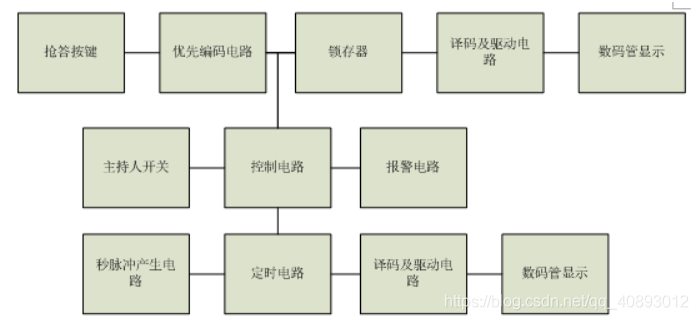

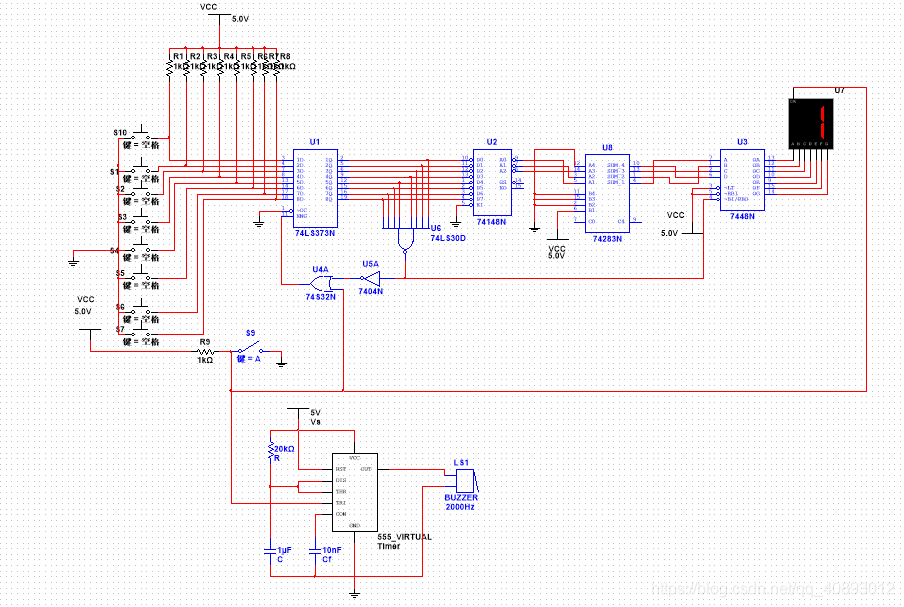

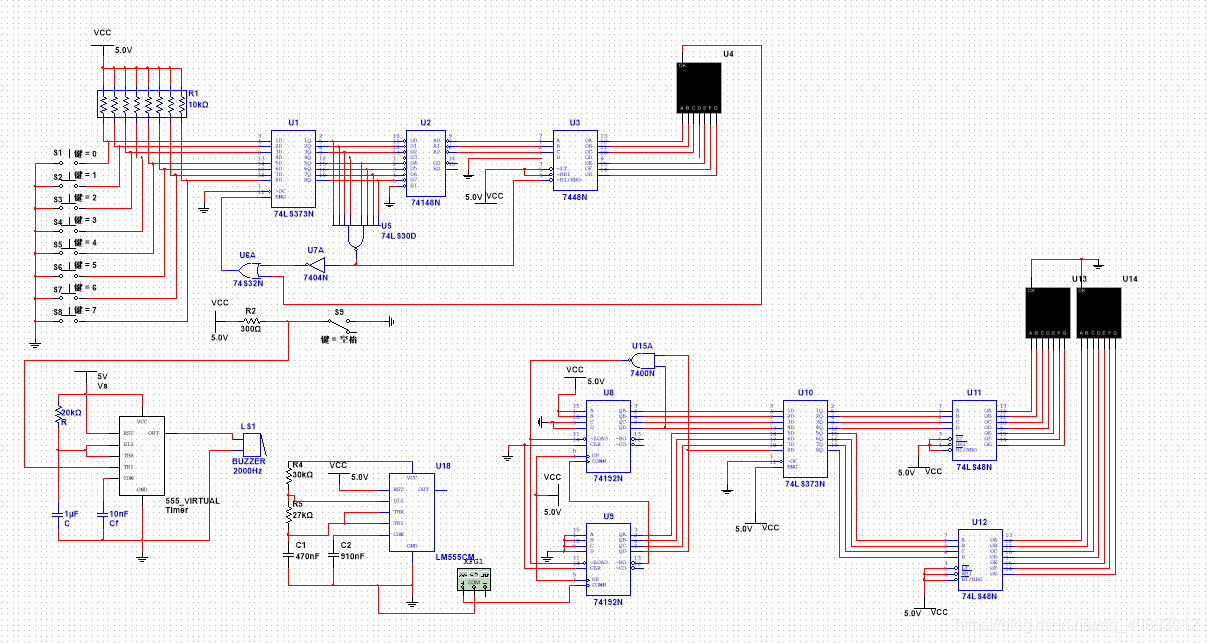

抢答电路、定时电路、报警电路在内的三部分电路组成。抢答电路由按键、锁存器、优先编码器、数码管译码驱动器等器件组成;定时电路由555定时器、计数器、锁存器、数码管译码驱动器、开关等器件组成;报警电路由蜂鸣器、单稳态脉冲触发芯片等器件组成。

1.2 工作框图

2 电路工作原理

2.1 抢答器电路

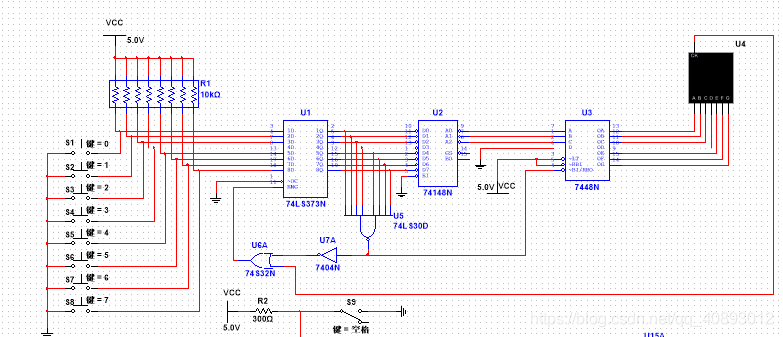

抢答器电路可以显示号数为0-7:

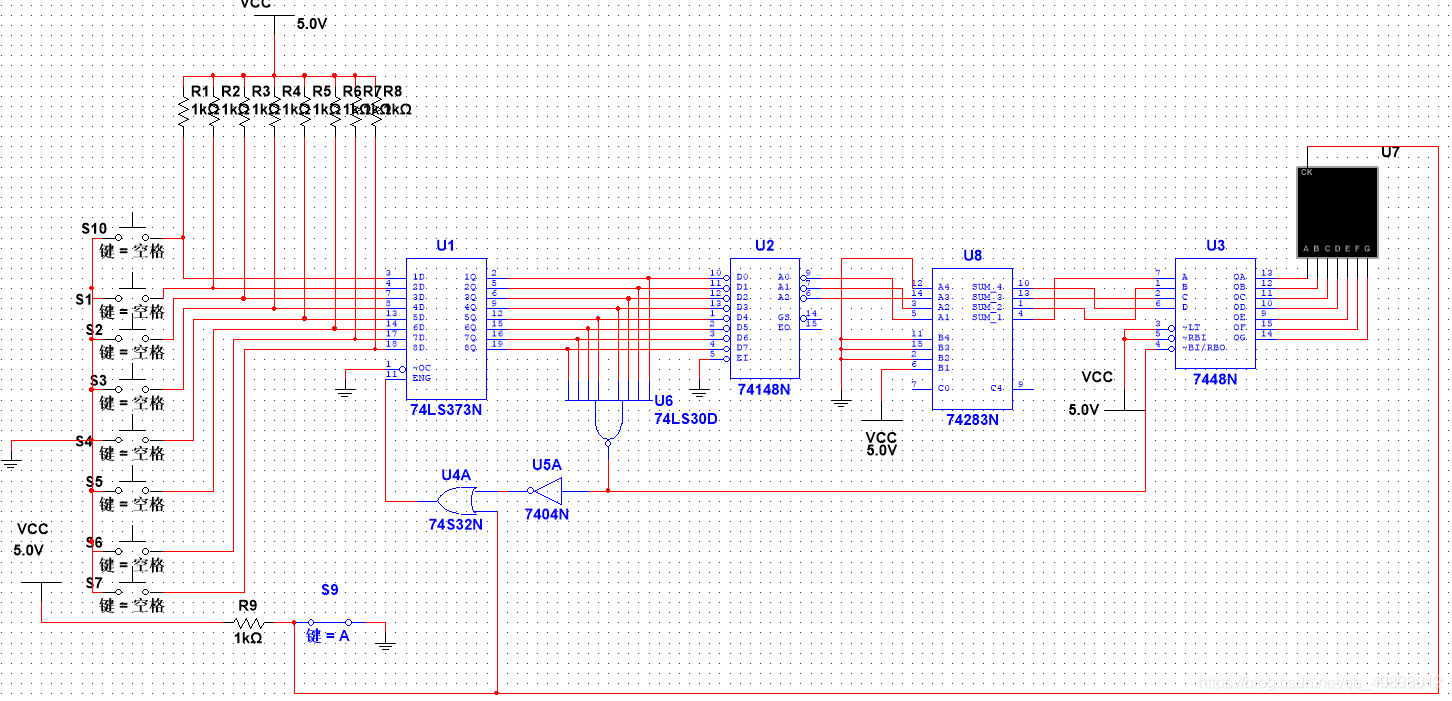

新的抢答器电路可以显示号数为1-8:直接替换旧的抢答器电路模块即可

当主持人控制开关S9处于断开状态时,74LS373的锁存控制端为高电平不锁存,Q随数据D而变。此时8输入与非门74LS30的输出为低电平。同时由于开关S9断开,数码管的共阴极为高电平,这样就不会在未抢答状态下显示号码了。而此时74148的输入为八个高电平输出为三个高电平如果不加控制经7448译码输出后会在数码管上显示数字7。这里把8输入与非门74ls30的输出接到7448的灭灯控制端BI/RBO,抑制数码管显示。当开关S9被闭合时,进入抢答状态。这时虽然开关S9闭合使或门74S32的一个输入端为0,但由于8输入与非门的输出仍为0所以74LS373的锁存控制端仍为1,不会阻止数据的通过。当第一个按键按下时,74LS30的输出变为高电平,同时由于开关S9以闭合使得或门74S32的两个输入都为低电平,则锁存器373的锁存控制端ENG变为低电平,锁存此时的Q值。理论上该值只有一个为低电平,其余为高电平,为低电平的那个即为抢答的成功的那个。这时对74148来说就有了有效输入(某个输入端变为0),优先编码得到一个数字作为7448的输入在数码管上显示出来。这样就完成了从抢答到显示的工作。

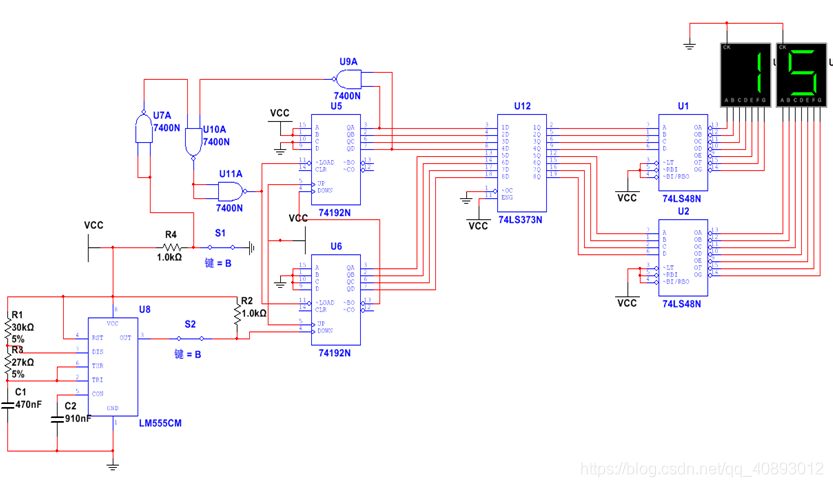

2.2 定时器电路

该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS19构成的减法计数电路、74LS4译码电路和2个7段数码管即相关电路组成。

其中555定时器和两个电阻、两个电容构成多谐振荡器产生周期为一秒的脉冲接到74LS192的减计数端进行每秒一次的减计数。其震荡周期的计算公式为 T = (R1+R2)C1*Ln2。在电路中R1 = 30K欧,R2 = 27K欧,C1 = 470nF,震荡周期为T = (30K+27K)*470nF*Ln2 = 1S。两片74LS192构成30进制减计数器。

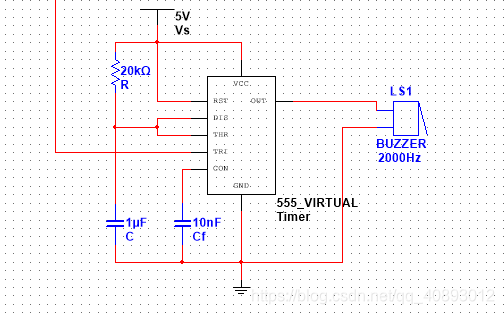

2.3 报警电路

当有脉冲到达时单稳态触发器进入暂稳态,输出高电平使蜂鸣器响进行发声报警。在暂稳态维持一段时间后,自动返回稳态回到低电平,蜂鸣器停止发声。将单稳态触发器的脉冲输入接到开关上,当开关闭合时产生一个脉冲使蜂鸣器发声。电路有TTL集成单稳态触发器构成。输出脉冲宽度公式为Tw =1.1RC。随着Tw宽度的增加,它的精度和稳定度也会随着下降这里R取20千欧姆,C取1uf。得到Tw约为0.2秒。当输入下降沿时蜂鸣器就会响0.2秒。

3 总体电路

此电路正常但是没有倒计时模块

此电路存在些许问题,倒计时模块存在问题

下载地址:https://github.com/HONOR-HRS/CSDN_CODE/tree/master/scrambler

百度云网盘下载 提取码:1234

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)