数字时钟仿真电路设计

课题设计要求时间以24小时为一个周期显示时、分、秒具有校时功能,可以分别对时分秒进行单独校时,使其校正到标准时间计时过程具有报时功能,当时间到达整点前十秒进行蜂鸣报时为了保证计时的稳定及准确,须由晶体振荡器提供表针时间基准信号准备工作查阅资料了解课题设计原理下载Multisim软件设计数字时钟仿真电路图仿真运行上机连线操作调试排查并改正错误与不足之处设计原理数字...

课题设计要求

- 时间以24小时为一个周期

- 显示时、分、秒

- 具有校时功能,可以分别对时分秒进行单独校时,使其校正到标准时间

- 计时过程具有报时功能,当时间到达整点前十秒进行蜂鸣报时

- 为了保证计时的稳定及准确,须由晶体振荡器提供表针时间基准信号

准备工作

- 查阅资料了解课题设计原理

- 下载Multisim软件

- 设计数字时钟仿真电路图

- 仿真运行

- 上机连线操作

- 调试排查并改正错误与不足之处

设计原理

数字电子时钟框架图

秒脉冲发生器

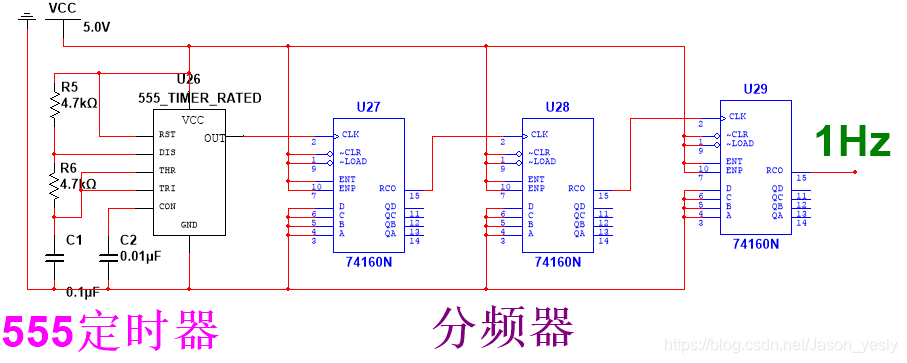

振荡器是计数器计数的关键,所以需要稳定的脉冲源,这里采用555定时器和电阻电容构成一个产生1kHz的电路,然后通过分频器分频得到 1Hz 的脉冲信号。而分频器本就是由计数器构成,所以这里采用3片74LS160级联组成一个分频器,每个芯片都是1/10分频,最终得到 1Hz的脉冲信号。

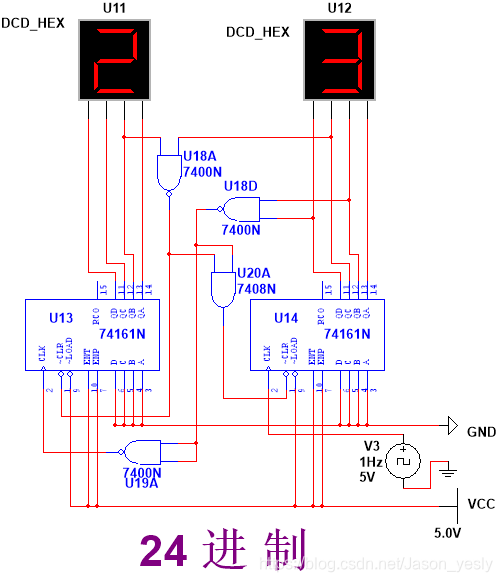

24进制的实现

本课题是用的2片74LS161芯片以及与非门实现24进制(00~23)。时计数器的十位是二进制,个位是十进制,同时和与非门相连,实现满24时清零。电路图如下图所示:

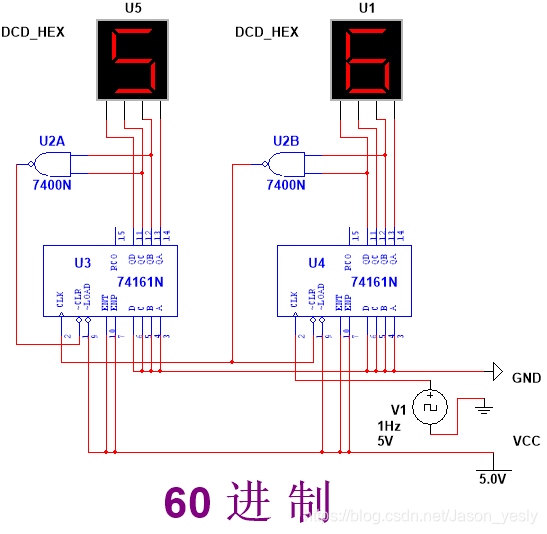

60进制的实现

分、秒都是60进制(00~59),所以它们的电路都是一样的,采用2片74LS161和与非门实现,分、秒计数器的十位都是 6进制,个位都是10进制,共同构成60进制。当记满59时,再来一个脉冲就清零变为00,接着再重新开始计数。

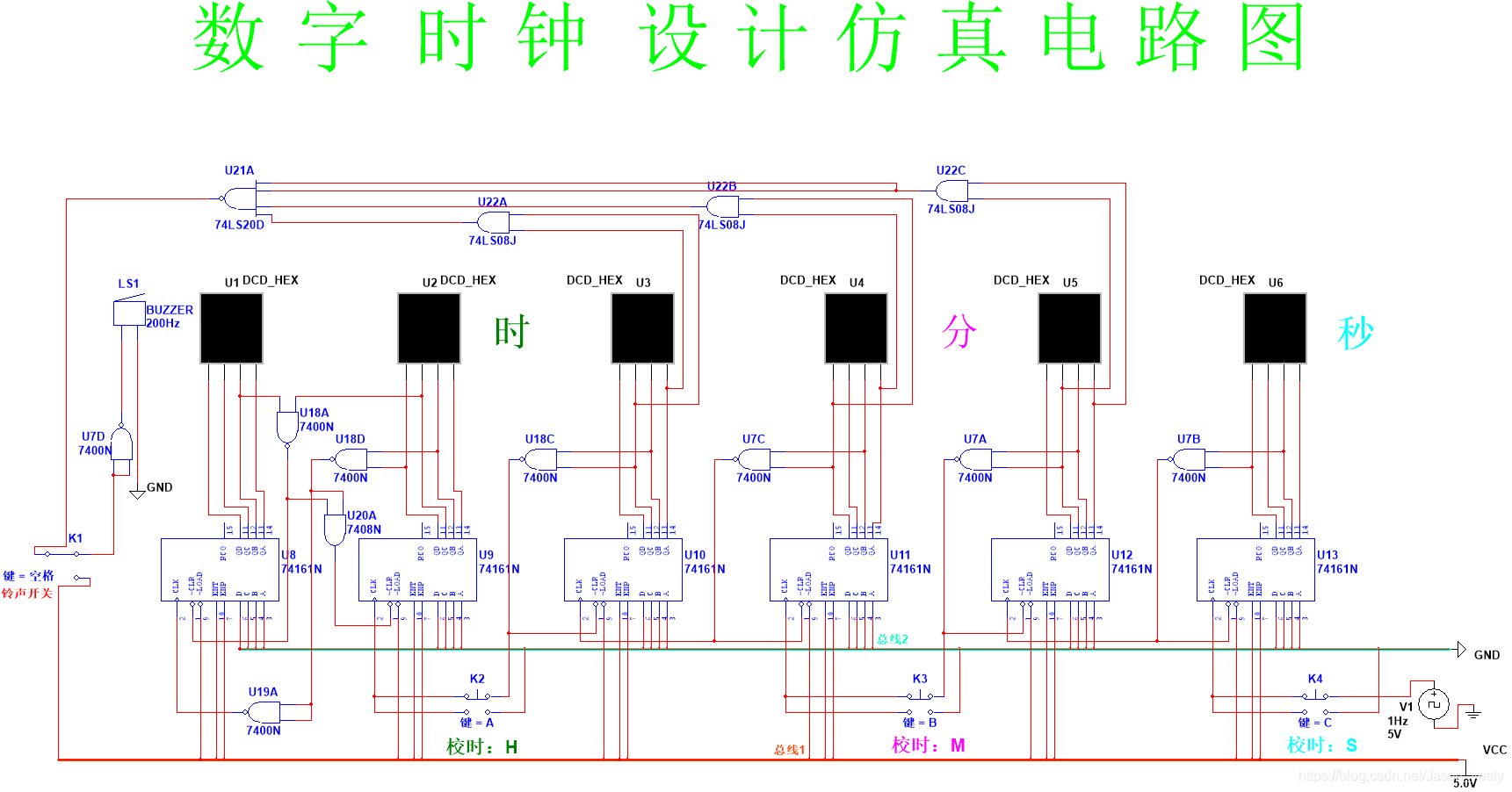

整点报时

课题设计要求整点前10s开始报时,这里主要是通过与非门实现,当分计数器计数为59且秒计数器的十位计数为5时开始报时,将分的两位及秒的十位分别用一个与门连接(对应接5、9、5),然后接一个与非门,与非门的输出端再次取反接蜂鸣器,就实现了报时功能(好像看起来有点繁琐,应该有更简单的方法)。

校时功能

用了最简单的方法,在分、秒的与非门与上一级的脉冲接口之间接一个开关即可。当开关按下时,产生一个低电平给计数器,从而在下降沿的时候计数器加一。

数字时钟电路仿真图

下面就是仿真图,图中的秒脉冲信号直接换成了一个小的脉冲,如果不用这个,可直接换成上面介绍的秒脉冲发生器电路代替。

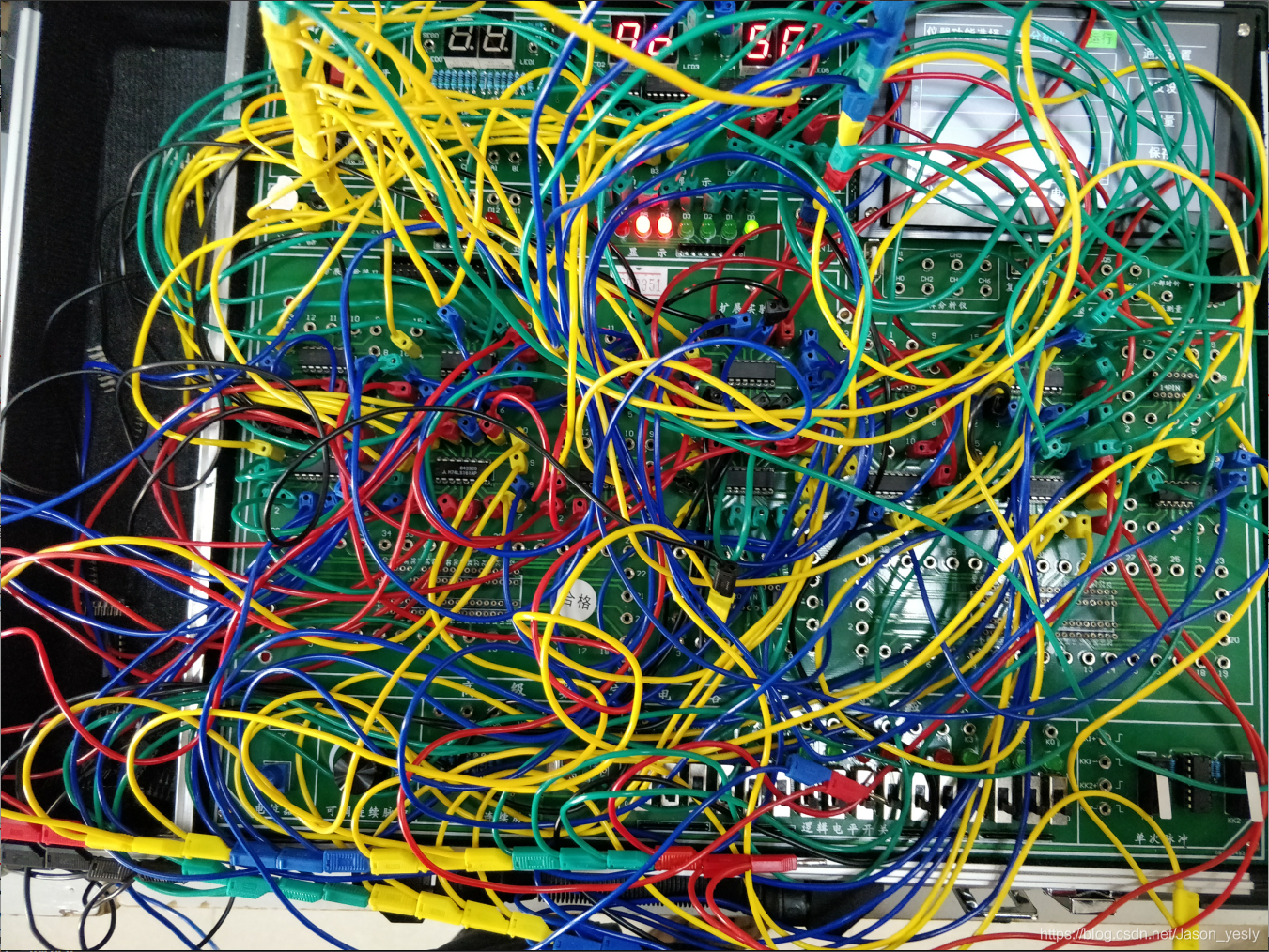

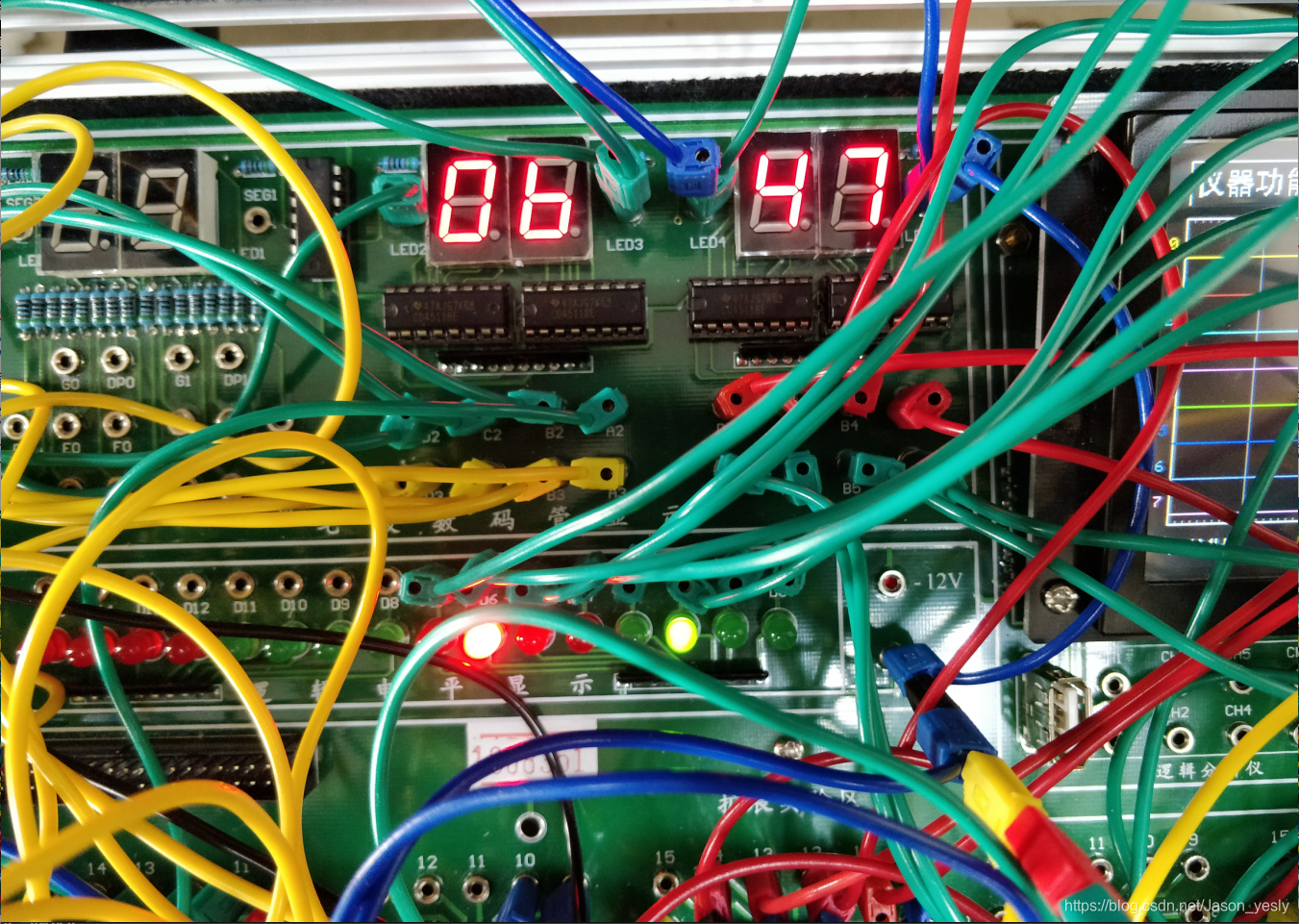

实验箱上组装调试

这玩意儿看着图不难,但真正在实验箱上组装的时候还是不容易啊,密密麻麻的线,一不留神就连错,找错也是很麻烦的,各种各样的问题,比如接线不稳,与非门的芯片有问题,或其他芯片问题都有可能出现。经过几个小时的奋战,总算是把它弄好了,下面是最后的效果图。

参考文章

数字钟设计

数字钟仿真

参考书:《数字电路实验及课程设计指导书》

电路设计使用的软件

主要使用Multisim进行仿真,软件安装教程:Multisim安装教程

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)