解密昇腾AI处理器--DaVinci架构(存储系统)

AI Core的片上存储单元和相应的数据通路构成了存储系统。众所周知,几乎所有的深度学习算法都是数据密集型的应用。对于昇腾AI芯片来说,合理设计的数据存储和传输结构对于最终系统运行的性能至关重要。不合理的设计往往成为性能瓶颈,从而白白浪费了片上海量的计算资源。AI Core通过各种类型分布式缓冲区之间的相互配合,为深度神经网络计算提供了大容量和及时的数据供应,为整体计算性能消除了数据流传输的瓶颈,

AI Core的片上存储单元和相应的数据通路构成了存储系统。众所周知,几乎所有的深度学习算法都是数据密集型的应用。对于昇腾AI芯片来说,合理设计的数据存储和传输结构对于最终系统运行的性能至关重要。不合理的设计往往成为性能瓶颈,从而白白浪费了片上海量的计算资源。AI Core通过各种类型分布式缓冲区之间的相互配合,为深度神经网络计算提供了大容量和及时的数据供应,为整体计算性能消除了数据流传输的瓶颈,从而支撑了深度学习计算中所需要的大规模、高并发数据的快速有效提取和传输。

存储单元

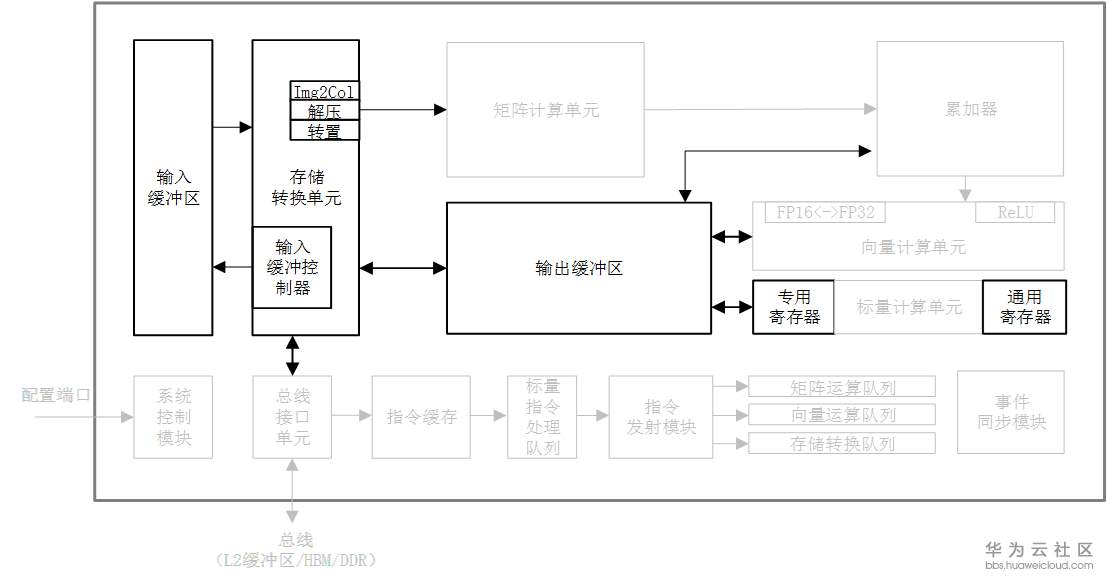

芯片中的计算资源要想发挥强劲算力,必要条件是保证输入数据能够及时准确的出现在计算单元里。达芬奇架构通过精心设计的存储单元为计算资源保证了数据的供应,相当于AI Core中的后勤系统。AI Core中的存储单元由存储控制单元、缓冲区和寄存器组成,如图3-11中的加粗显示。存储控制单元通过总线接口可以直接访问AI Core之外的更低层级的缓存,并且也可以直通到DDR或HBM从而可以直接访问内存。存储控制单元中还设置了存储转换单元,其目的是将输入数据转换成AI Core中各类型计算单元所兼容的数据格式。缓冲区包括了用于暂存原始图像特征数据的输入缓冲区,以及处于中心的输出缓冲区来暂存各种形式的中间数据和输出数据。AI Core中的各类寄存器资源主要是标量计算单元在使用。

所有的缓冲区和寄存器的读写都可以通过底层软件显式的控制,有经验的程序员可以通过巧妙的编程方式来防止存储单元中出现读写冲突而影响流水线的进程。对于类似卷积和矩阵这样规律性强的计算模式,高度优化的程序可以实现全程无阻塞的流水线执行。

上图中的总线接口单元作为AI Core的“大门”,是一个与系统总线交互的窗口,并以此通向外部世界。AI Core通过总线接口从外部L2缓冲区、DDR或HBM中读取或者写回数据。总线接口在这个过程中可以将AI Core内部发出的读写请求转换为符合总线要求的外部读写请求,并完成协议的交互和转换等工作。

输入数据从总线接口读入后就会经由存储转换单元进行处理。存储转换单元作为AI Core内部数据通路的传输控制器,负责AI Core内部数据在不同缓冲区之间的读写管理,以及完成一系列的格式转换操作,如补零,Img2Col,转置、解压缩等。存储转换单元还可以控制AI Core内部的输入缓冲区,从而实现局部数据的缓存。

在深度神经网络计算中,由于输入图像特征数据通道众多且数据量庞大,往往会采用输入缓冲区来暂时保留需要频繁重复使用的数据,以达到节省功耗、提高性能的效果。当输入缓冲区被用来暂存使用率较高的数据时,就不需要每次通过总线接口到AI Core的外部读取,从而在减少总线上数据访问频次的同时也降低了总线上产生拥堵的风险。另外,当存储转换单元进行数据的格式转换操作时,会产生巨大的带宽需求,达芬奇架构要求源数据必须被存放于输入缓冲区中,才能够进行格式转换,而输入缓冲控制器负责控制数据流入输入缓冲区中。输入缓冲区的存在有利于将大量用于矩阵计算的数据一次性的被搬移到AI Core内部,同时利用固化的硬件极高的提升了数据格式转换的速度,避免了矩阵计算单元的阻塞,消除了由于数据转换过程缓慢而带来的性能瓶颈。

在神经网络中往往可以把每层计算的中间结果放在输出缓冲区中,从而在进入下一层计算时方便的获取数据。由于通过总线读取数据的带宽低,延迟大,通过充分利用输出缓冲区就可以大大提升计算效率。

在矩阵计算单元还包含有直接的供数寄存器,提供当前正在进行计算的大小为16*16的左、右输入矩阵。在矩阵计算单元之后,累加器也含有结果寄存器,用于缓存当前计算的大小为16*16的结果矩阵。在累加器配合下可以不断的累积前次矩阵计算的结果,这在卷积神经网络的计算过程中极为常见。在软件的控制下,当累积的次数达到要求后,结果寄存器中的结果可以被一次性的传输到输出缓冲区中。

AI Core中的存储系统为计算单元提供源源不断的数据,高效适配计算单元的强大算力,综合提升了AI Core的整体计算性能。与谷歌TPU设计中的统一缓冲区设计理念相类似,AI Core采用了大容量的片上缓冲区设计,通过增大的片上缓存数据量来减少数据从片外存储系统搬运到AI Core中的频次,从而可以降低数据搬运过程中所产生的功耗,有效控制了整体计算的能耗。

达芬奇架构通过存储转换单元中内置的定制电路,在进行数据传输的同时,就可以实现诸如Im2Col或者其它类型的格式转化操作,不光是节省了格式转换过程中的消耗,同时也节省了数据转换的指令开销。这种能将数据在传输的同时进行转换的指令称为随路指令。硬件单元对随路指令的支持为程序设计提供了便捷性。

数据通路

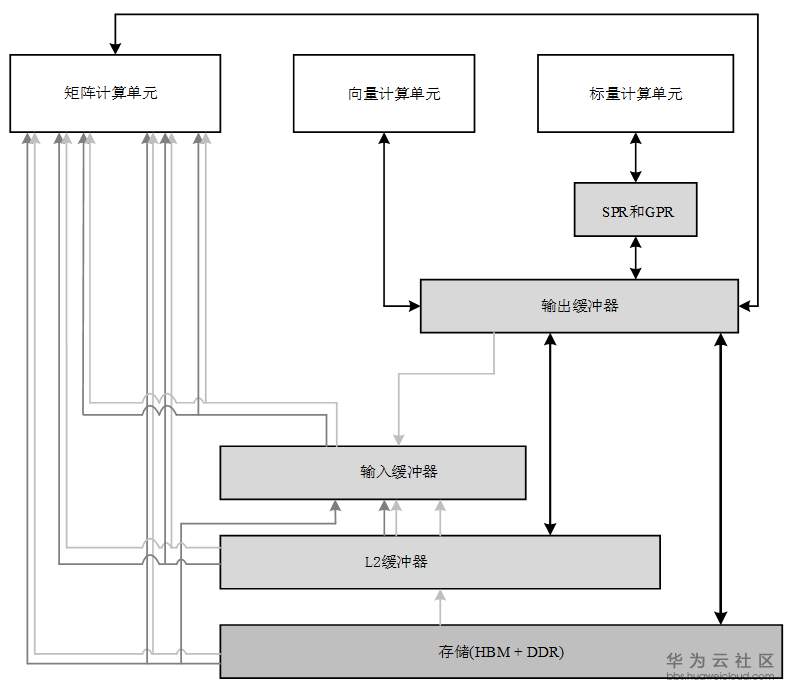

数据通路指的是AI Core在完成一个计算任务时,数据在AI Core中的流通路径。前文已经以矩阵相乘为例简单介绍了数据的搬运路径。图3-12展示了达芬奇架构中一个AI Core内完整的数据传输路径。这其中包含了DDR或HBM,以及L2缓冲区,这些都属于AI Core核外的数据存储系统。图中其它各类型的数据缓冲区都属于核内存储系统。

核外存储系统中的数据可以通过LOAD指令被直接搬运到矩阵计算单元中进行计算,输出的结果会被保存在输出缓冲区中。除了直接将数据通过LOAD指令发送到矩阵计算单元中,核外存储系统中的数据也可以通过LOAD指令先行传入输入缓冲区,再通过其它指令传输到矩阵计算单元中。这样做的好处是利用大容量的输入缓冲区来暂存需要被矩阵计算单元反复使用的数据。

矩阵计算单元和输出缓冲区之间是可以相互传输数据的。由于矩阵计算单元容量较小,部分矩阵运算结果可以写入输出缓冲区中,从而提供充裕的空间容纳后续的矩阵计算。当然也可以将输出缓冲区中的数据再次搬回矩阵计算单元作为后续计算的输入。输出缓冲区和向量计算单元、标量计算单元以及核外存储系统之间都有一条独立的双向数据通路。输出缓冲区中的数据可以通过专用寄存器或通用寄存器进出标量计算单元。

值得注意的是,AI Core中的所有数据如果需要向外部传输,都必须经过输出缓冲区,才能够被写回到核外存储系统中。例如输入缓冲区中的图像特征数据如果需要被输出到系统内存中,则需要先经过矩阵计算单元处理后存入输出缓冲区中,最终从输出缓冲区写回到核外存储系统中。在AI Core中并没有一条从输入缓冲区直接写入到输出缓冲区的数据通路。因此输出缓冲区作为AI Core数据流出的闸口,能够统一的控制和协调所有核内数据的输出。

达芬奇架构数据通路的特点是多进单出,数据流入AI Core可以通过多条数据通路,可以从外部直接流入矩阵计算单元、输入缓冲区和输出缓冲区中的任何一个,流入路径的方式比较灵活,在软件的控制下由不同数据流水线分别进行管理。而数据输出则必须通过输出缓冲区,最终才能输出到核外存储系统中。

这样设计的理由主要是考虑到了深度神经网络计算的特征。神经网络在计算过程中,往往输入的数据种类繁多并且数量巨大,比如多个通道、多个卷积核的权重和偏置值以及多个通道的特征值等,而AI Core中对应这些数据的存储单元可以相对独立且固定,可以通过并行输入的方式来提高数据流入的效率,满足海量计算的需求。AI Core中设计多个输入数据通路的好处是对输入数据流的限制少,能够为计算源源不断的输送源数据。与此相反,深度神经网络计算将多种输入数据处理完成后往往只生成输出特征矩阵,数据种类相对单一。根据神经网络输出数据的特点,在AI Core中设计了单输出的数据通路,一方面节约了芯片硬件资源,另一方面可以统一管理输出数据,将数据输出的控制硬件降到最低。

综上,达芬奇架构中的各个存储单元之间的数据通路以及多进单出的核内外数据交换机制是在深入研究了以卷积神经网络为代表的主流深度学习算法后开发出来的,目的是在保障数据良好的流动性前提下,减少芯片成本、提升计算性能、降低控制复杂度。

更多内容,请关注昇腾开发者社区

作者:Torrenza

更多推荐

已为社区贡献6297条内容

已为社区贡献6297条内容

所有评论(0)